# **Combinational Building Blocks**

Prof. Dr. Miloš Krstić

### **Multi-valued Logic**

- Example Three-State Buffer

- We can define the types with different values type tri is ('0','1','Z');

The signal can be then defined as Signal a, b, c: tri;

- How to use tri same as bit signals?

For example how to calculate:

B<= a and c after 5 ns;</li>

- Defining the function

| AND | 0 | 1 | Z |

|-----|---|---|---|

| 0   | 0 | 0 | 0 |

| 1   | 0 | 1 | 1 |

| Z   | 0 | 1 | Z |

#### **Overloading Operator**

We can define function which can overload standard operators (such as and)

We cannot mix different operators now! (for example bit and tri)

Overloading must be used very carefully

#### **Standard Logic Type**

Normally the logic implemented in hardware is modelled with more than

```

binary values ('0' and '1')

'Z' -high impedance

'L' - weak 0

'H' - weak 1

'U' - undefined

'X' - strong unknown

'W' - weak unknown

'-' - don't care

type std ulogic is ('U','X','0','1','Z','W','L','H','-');

How AND truth table for std ulogic could be defined?

subtype std_logic is resolved std_ulogic;

Standard types and functions are organized in a package

We have to use them from the library

library IEEE;

```

```

use IEEE.std_logic_1164.all;

```

#### **Building Three State Buffer**

EN

```

library IEEE;

use IEEE.std_logic_1164.all;

entity three_state is

port (a, enable : in std_logic;

z : out std_logic);

end entity three_state;

architecture when_else of three_state is

begin

z <= a when enable = '1' else 'Z';

end architecture when_else;

architecture after_when_else of three_state is

begin

z <= a after 4 NS when enable = '1' else 'Z';

end architecture after_when_else;

```

#### **Decoder**

Converts data into some other form

| In         | puts | Outputs    |           |            |            | BIN/I | -OF-4 |

|------------|------|------------|-----------|------------|------------|-------|-------|

| <b>A</b> 1 |      | <b>Z</b> 3 | <b>Z2</b> | <b>Z</b> 1 | <b>Z</b> 0 | 1     | 1     |

| 0          | 0    | 0          | 0         | 0          | 1          |       | 2     |

| 0          | 1    | 0          | 0         | 1          | 0 _        | 2     | 3     |

| 1          | 0    | 0          | 1         | 0          | 0          |       | 4     |

| 1          | 1    | 1          | 0         | 0          | 0          |       |       |

How to define vectors in VHDL

type std\_logic\_vector is array (natural range <>) of std\_logic;

One possibility for implementation is library IEEE; use IEEE.std\_logic\_1164.all; entity decoder is port (a : in std\_logic\_vector(1 downto 0); z : out std\_logic\_vector(3 downto 0)); end entity decoder; architecture when\_else of decoder is begin  $z \le 0001$ " when a = 00" else "0010" when a = 01" else "0100" when a = "10" else "1000" when a = "11" else "XXXX"; end architecture when\_else;

```

library IEEE;

use IEEE.std_logic_1164.all;

entity decoder is

port (a : in std_logic_vector(1 downto 0);

z : out std_logic_vector(3 downto 0));

end entity decoder;

architecture with_select of decoder is

begin

with a select

z <= "0001" when "00",

"0010" when "01",

"0100" when "10",

"1000" when "11",

"XXXX" when others;

end architecture with_select;

```

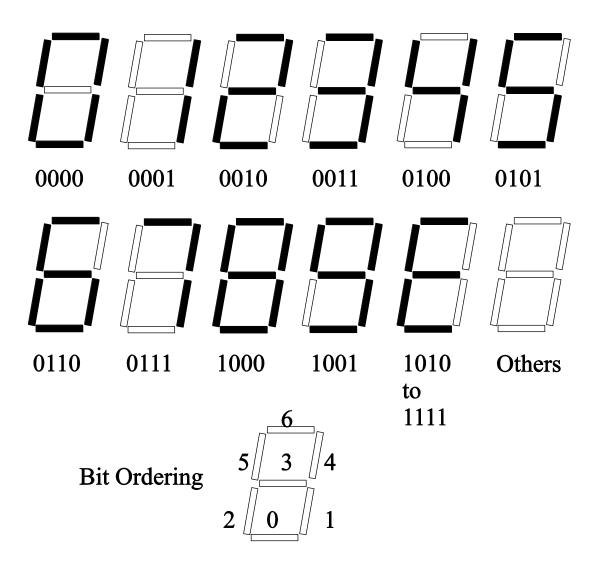

## **Practical example - Seven Segment Decoder**

## Please try at home and in labs!

How to ensure parametric design?

Use of generics is essential in VHDL

```

entity decoder is

generic (n : POSITIVE);

port (a : in std_logic_vector(n-1 downto 0);

z : out std_logic_vector(2**n-1 downto 0));

end entity decoder;

```

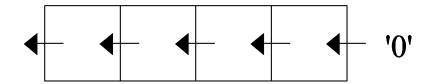

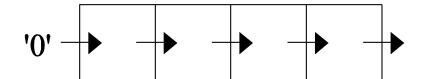

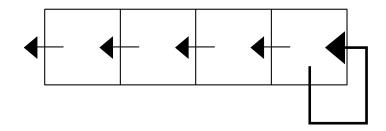

## **VHDL Shift Operators**

sll

srl

sla

sra

rol

ror

#### **Types of Arithmetic and Conversion in VHDL**

- Standard std\_logic\_1164 package supports std\_logic\_vectors and integers

For conversion one can use to\_StdLogicVector and to\_integer functions

- For arithmetic we need definition whether this is signed or unsigned

This is supported by numeric\_std package

```

Conversion std_logic_vector ⇔ (un) signed is simple x<= unsigned(y); y<= std_logic_vector(x);

```

From integer we need to define the number of bits: to\_unsigned(i,n)

Take care about the number of bits when using integers!

#### **Multiplexers**

Multiplexer switches one of many inputs to a single output

They enable effective reuse of hardware

```

entity mux is

port (a, b, c, d: in std_logic;

s: in std_logic_vector(1 downto 0);

y: out std_logic);

end entity mux;

architecture mux1 of mux is

begin

with s select

y <= a when "00",

b when "01",

c when "10",

d when "11",

'X' when others;

end architecture mux1;

```

```

\begin{array}{c}

MUX \\

0 \\

1 \\

0 \\

0 \\

1 \\

2 \\

3

\end{array}

```

## **Priority Encoders**

In many situations the output of the combinational block is irrelevant to the complete set of inputs

In this case we can use don't care values

## **Example priority encoder**

| Inputs     |           |           |           | Outp      | uts       |       |

|------------|-----------|-----------|-----------|-----------|-----------|-------|

| <b>A</b> 1 | <b>A2</b> | <b>A3</b> | <b>A4</b> | <b>Y1</b> | <b>Y0</b> | Valid |

| 0          | 0         | 0         | 0         | 0         | 0         | 0     |

| 0          | 0         | 0         | 1         | 0         | 0         | 1     |

| 0          | 0         | 1         | -         | 0         | 1         | 1     |

| 0          | 1         | -         | -         | 1         | 0         | 1     |

| 1          | -         | -         | -         | 1         | 1         | 1     |

#### **Priority Encoder - Implementation**

```

library IEEE;

HPRI/BIN

use IEEE.std_logic_1164.all;

entity priority is

0/Z10

port (a: in std_logic_vector(3 downto 0);

y: out std_logic_vector(1 downto 0);

1/Z11

valid: out std_logic);

end entity priority;

2/Z12 12

3/Z13 13

architecture DontCare of priority is

begin

with a select

y <= "00" when "0001",

"01" when "001-",

"10" when "01--",

"11" when "1---",

"00" when others;

```

else '0':

end architecture DontCare;

valid  $\leftarrow$  '1' when a(0)='1' or a(1)='1' or a(2)='1' or a(3) = '1'

## **Priority Encoder – Alternative Implementation**

```

HPRI/BIN

library IEEE;

0/Z10

use IEEE.std_logic_1164.all;

entity priority is

1/Z11

port (a: in std_logic_vector(3 downto 0);

y: out std_logic_vector(1 downto 0);

2/Z12 12

valid: out std_logic);

3/Z13 13

end entity priority;

architecture Ordered of priority is

begin

y <= "11" when a(3)='1' else

"10" when a(2)='1' else

"01" when a(1)='1' else

"00" when a(0)='1' else

"00":

valid \leftarrow '1' when a(0)='1' or a(1)='1' or a(2)='1' or a(3) = '1'

else '0';

```

end architecture Ordered;

#### **VHDL Modelling Styles**

Three ways of VHDL coding, two have been covered before Structural – netlist type

```

u1: inv port map (A, X);

```

Dataflow – concurrent signal assignments out <= '0' when In1=In2 else '1';

**Sequential – can be used in functions, procedures and processes**

Process – one of the most important structures in VHDL Sensitivity list if statements

#### **Priority Encoder – sequential Implementation**

```

library IEEE;

use IEEE.std_logic_1164.all;

entity priority is port (a: in std_logic_vector(3 downto 0); y: out std_logic_vector(1 downto 0); valid: out

std logic); end entity priority;

architecture Sequential of priority is

begin

process (a) is

begin

if a(3)='1' then

y <= "11"; valid <= '1';

HPRI/BIN

elsif a(2)='1' then

y <= "10"; valid <= '1';

0/Z10 10

elsif a(1)='1' then

y <= "01"; valid <= '1';

1/Z11

11

elsif a(0)='1' then

2/Z12 12

y <= "00"; valid <= '1';

else

3/Z13 13

y <= "00"; valid <= '0';

end if;

end process;

```

end architecture Sequential;

#### **Adders**

Entity declaration

library IEEE;

use IEEE.std\_logic\_1164.all, IEEE.numeric\_std.all;

entity NBitAdder is

generic (n: NATURAL :=4);

port(A, B: in std\_logic\_vector(n-1 downto 0);

Cin: in std\_logic;

Sum: out std\_logic\_vector(n-1 downto 0);

Two types of addition

end entity NBitAdder;

Cout: out std\_logic);

Signed Unsigned

CO

## **Adders – Unsigned Implementation**

```

architecture unsgned of NBitAdder is

signal result : unsigned(n downto 0);

signal carry : unsigned(n downto 0);

constant zeros : unsigned(n-1 downto 0) := (others => '0');

begin

carry <= (zeros & Cin);</pre>

result <= ('0' & unsigned(A)) + ('0' & unsigned(B)) + carry;

Sum <= std_logic_vector(result(n-1 downto 0));</pre>

Cout <= result(n);

end architecture unsgned;

```

## **Adders – Signed Implementation**

```

architecture sgned of NBitAdder is

signal result : signed(n downto 0);

signal carry : signed(n downto 0);

constant zeros : signed(n-1 downto 0) := (others => '0');

begin

carry <= (zeros & Cin);</pre>

result \leq (A(n-1) & signed(A)) + (B(n-1) & signed(B)) + carry;

Sum <= std_logic_vector(result(n-1 downto 0));</pre>

Cout <= result(n);

end architecture sgned;

CO

```

#### **Single Bit Full Adder**

```

library IEEE;

use IEEE.std_logic_1164.all;

entity FullAdder is

port (a, b, Cin : in std_logic; Sum, Cout: out std_logic);

end entity FullAdder;

architecture concurrent of FullAdder is

begin

Sum <= a xor b xor Cin;

Cout <= (a and b) or (a and Cin) or (b and Cin);

end architecture concurrent;

```

Two assignments are concurrent!

This is a general rule in VHDL

#### **Adder – Iterative Implementation**

```

architecture StructIterative of NBitAdder is

signal Carry: std_logic_vector(0 to n);

begin

g1: for i in 0 to n-1 generate

It: if i = 0 generate

f0 : entity work.FullAdder port map (A(i), B(i), Cin, Sum(i), Carry(i+1));

end generate It;

rt : if i = n-1 generate

fn : entity work.FullAdder port map (A(i), B(i), Carry(i), Sum(i), Cout);

end generate rt;

md: if i > 0 and i < n-1 generate

fm : entity work.FullAdder port map (A(i), B(i), Carry(i), Sum(i), Carry(i+1));

end generate md;

end generate g1;

end architecture StructIterative;

```

## **Parity Checker**

```

library IEEE;

use IEEE.std_logic_1164.all;

2k

entity parity is

port (a : in std_logic_vector;

y : out std_logic);

end entity parity;

architecture iterative of parity is

begin

process (a) is

variable even : std_logic;

begin

even := '0';

for i in a'RANGE loop

if a(i) = '1' then

New VHDL constructs

attribute RANGE

even := not even;

use of variables

end if;

end loop;

Immediately Update

for loop

y <= even;

Principle of loop unrolling

end process;

end architecture iterative;

```

#### **Testbenches for Combinational Blocks**

#### Two important functions of a testbench

Generation of input stimuli Checking of results validity

#### Example Adder testbench

```

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.numeric_std.all;

entity TestNBitAdder is

end entity TestNBitAdder;

architecture TestBench_1 of TestNBitAdder is

constant n: NATURAL := 4;

signal A, B, Sum: std_logic_vector (n-1 downto 0);

signal Cin, Cout: std_logic;

begin

s0: entity WORK.NBitAdder(unsgned) generic map (n) port map(A, B, Cin, Sum, Cout);

Cin <= '0', '1' after 10 NS, '0' after 25 NS;

A <= "0000", "1111" after 5 NS, "0111" after 15 NS;

B <= "0000", "1111" after 20 NS;

end architecture TestBench_1;

```

#### **Testbenches in a Process**

```

architecture TestBench_3 of TestNBitAdder is

constant n: NATURAL := 4;

signal A, B, Sumint: NATURAL;

signal Aslv, Bslv, Sum: std_logic_vector (n-1 downto 0);

signal Cin, Cout: std_logic;

begin

s0: entity WORK.NBitAdder(unsgned) generic map (n) port map(Aslv, Bslv, Cin, Sum, Cout);

Aslv <= std_logic_vector(to_unsigned(A, n)); Bslv <= std_logic_vector(to_unsigned(B, n));

Sumint <= to_integer(unsigned(Cout & Sum));</pre>

stim: process is

begin

Cin <= '0';

A \le 0:

B <= 0;

wait for 5 NS;

A <= 15;

wait for 5 NS;

Cin <= '1';

wait for 5 NS;

A <= 7;

wait for 5 NS;

B <= 15;

wait for 5 NS;

Cin <= '0';

wait;

end process;

end architecture TestBench_3;

```

```

architecture TestBench_4 of TestNBitAdder is

constant n: NATURAL := 4;

signal A, B, Sumint: NATURAL; signal Aslv, Bslv, Sum: std_logic_vector (n-1 downto 0);

signal Cin, Cout: std_logic; signal error: BOOLEAN := FALSE;

begin

s0: entity WORK.NBitAdder(unsgned) generic map (n) port map(Aslv, Bslv, Cin, Sum, Cout);

Aslv <= std_logic_vector(to_unsigned(A, n));

Bslv <= std logic vector(to unsigned(B, n));

Sumint <= to_integer(unsigned(Cout & Sum));</pre>

stim: process is

begin

Cin <= '0'; A <= 0; B <= 0;

wait for 5 NS;

A <= 15:

wait for 5 NS;

Cin <= '1';

wait for 5 NS;

A <= 7;

wait for 5 NS;

B <= 15;

wait for 5 NS;

Cin <= '0';

wait;

end process;

resp: process (Cout, Sum) is

begin

error <= (A + B + BIT'POS(to_bit(Cin))) /= Sumint;

end process;

end architecture TestBench 4;

```

#### **Conclusions**

- We have learnt a number of basic combinational logic blocks

- In order to define them several VHDL constructs have been introduced

**Packages**

When...else

With...select

Generate

**Shift operators**

**Processes**

Testbench generation is also presented